Peripheral Component Interconnect Express(PCI Express ), abbreviated as PCIe or PCI-e. It is a bus standard and also called high-speed serial computer bus standard, it substituted the older PCI, AGP and PCI-X bus standards. It is the common interface for personal computers with motherboards.

Ex:- Graphic Card, HDDs, SSDs, Wi-Fi, and Ethernet hardware connections.

What is PCIe Lanes

An interconnect or link is a logical connection that enables communication between PCI Express devices. A link is a point-to-point communication channel that connects two PCI Express ports, enabling them to exchange routine PCI requests including configuration, I/O or memory read/write requests, and interrupts.

A lane consists of two differential signalling pairs, one of which is used for receiving data and the other for transmitting data. Each lane is made up of four wires or signal traces as a result. Each lane is conceptually utilised as a full-duplex byte stream, sending and receiving data packets in an eight-bit “byte” format back and forth between connection ends.

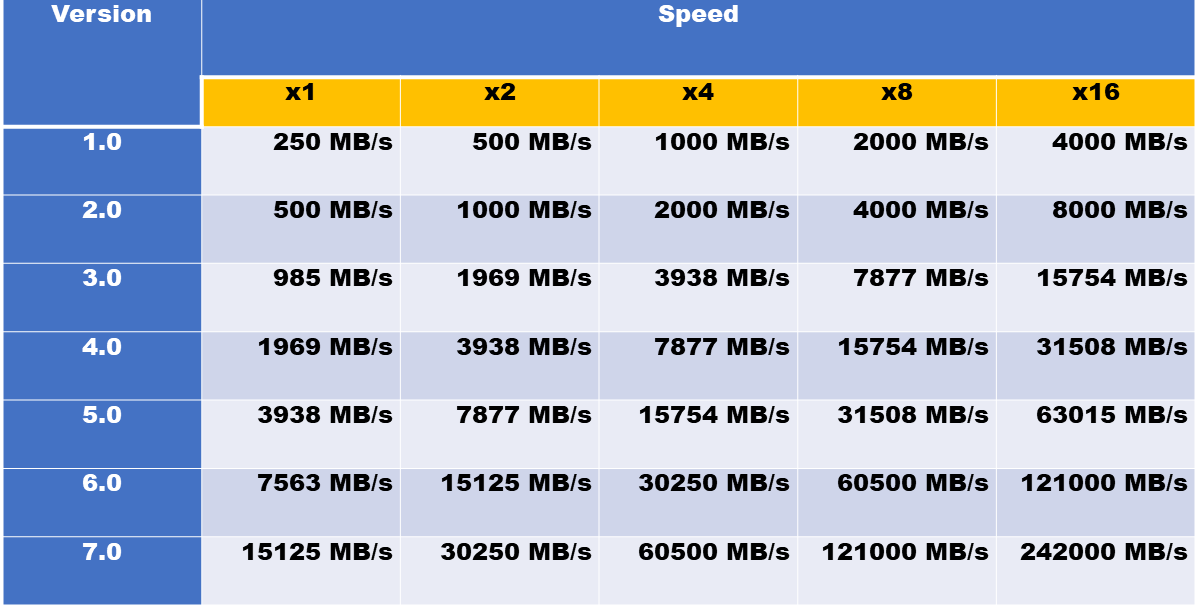

Physical PCI Express links can be 1, 4, 8, or 16 lanes in length. 4, 5 The greatest size that is typically used for lane counts is “x16,” with other sizes denoted by a “x” prefix (for instance, “x8” signifies an eight-lane card or slot). The phrases “width” or “by” are also used to describe lane sizes, so an eight-lane space can be referred to as “8 lanes wide” or “a by 8.”

. Link between two devices consists of one or more lanes is called PCI Express lanes, These lanes are dual simplex channels using two differential signaling pairs. A lane is a single send/receive line of data. The interface is also called ExpressCard used in a variety of other standards, most particularly the laptop expansion card interface. PCI Express is also used in the storage interfaces of SATA, and M.2

Each lane moves the data at 1 bit per cycle at least. The actual speed at which the data is transferred across a lane is determined by the CPU as well as the PCIe version.

PCIe Gen Max Speed

what is pci express link state power management

Up to 3 A at +3.3 V may be consumed by all PCI express cards (9.9 W). The form factor and function of the card will determine how much +12 V and overall power they may use:

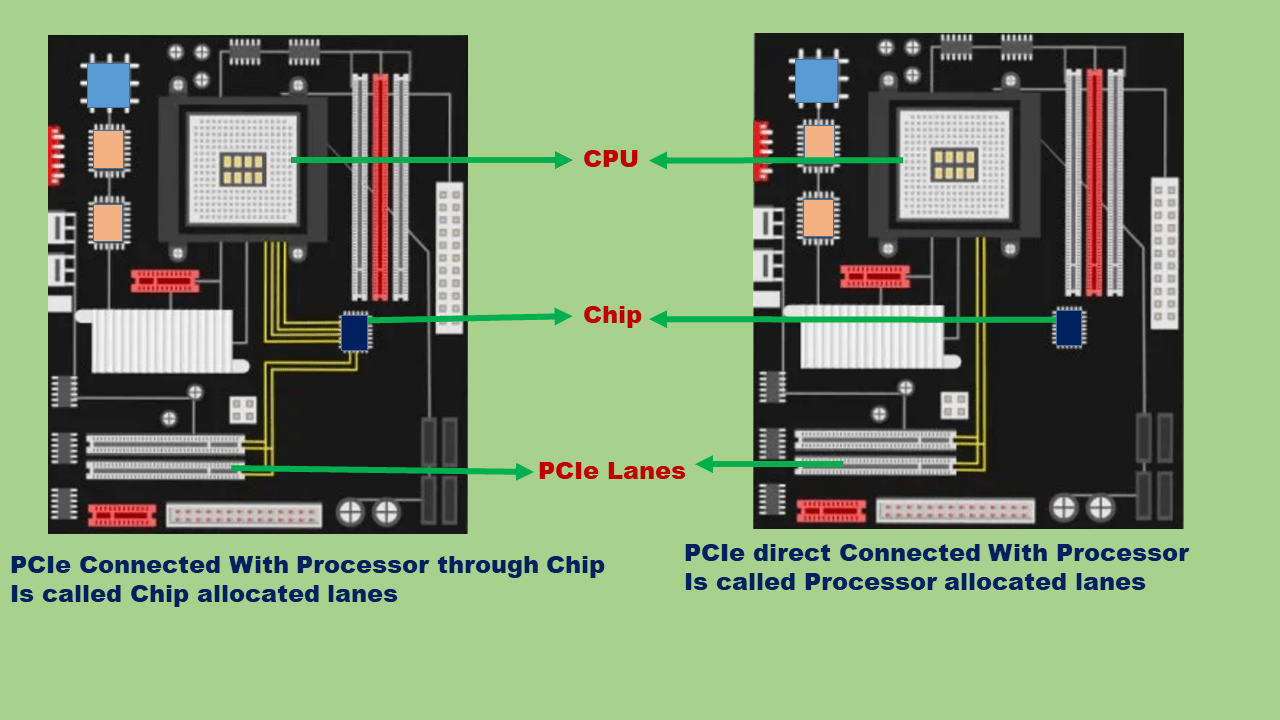

An x4 device will operate at 4 bits per cycle yet take up 4 PCIe lanes if an x1 device operates at 1 bit per cycle.A typical graphics card uses 16 PCIe lanes because it is an x16 device.The number of PCIe lanes varies based on the generation, make, and model of your CPU. A typical Intel Core series CPU from the 10th and lower generations, for example, has 16 lanes. The x16 slot is connected to all 16 lanes.

Processor vs Chipset allocated PCIe lanes

20PCIe Lanes Means

In Intel Processors 11th Gen CPU, have 20 PCIe lanes. 16 of these connect to an x16 slot and the rest of 4 lanes connect to an M.2 slot.

How Many PCIe Lanes Does M.2 Slot Use?

Normally M.2 uses 4 PCIe lanes for installing NVMe SSDs. Sometimes, on particular motherboards you can also find M.2 slots connected to only 2 PCIe lanes. 2 PCIe lane M.2 slots will operate the NVMe SSDs at half the speeds.

What is Boost Clock and Base Clock (Clock Rate) in CPU?

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Express 4.0 x16 […]

[…] incorporate hot-swapping hard drive slots for NVMe SSDs, which connect directly to the CPU using PCIe Gen5. This direct connection ensures optimal NVMe performance, facilitating a plug-and-play experience […]

[…] enable SSDs with sequential read/write speeds of 12 GB/s and higher, particularly when paired with PCIe 5.0 x4 […]

[…] PCI Express Version […]

[…] Generation Storage: 4*PCIe 4.0 x4 M.2 […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Express Version […]

[…] PCI Express Version […]

[…] PCI Express Version […]

[…] not intended for legacy protocols like SAS. Due to its speed and proximity to the CPU, PCI Express (PCIe), on which NVMe is based, became the next logical storage interface. By distributing flash […]

[…] employing the most recent Dell servers and 4th generation Intel Xeon Processors with increased PCIe bandwidth and improved network capabilities showed over 6x higher performance and up to 4.9x lower […]

[…] out our list of the Best SSDs for additional information on some of the most impressive PCIe Gen 5 solid state drives. To be clear, the SSD7749E does not support PCIe Gen 5 speeds and only […]

[…] industrial-grade storage and memory solutions. The T425 supports PCIe Gen 3 and NVMe 1.3 across two PCIe lanes and is offered in the M.2 2230 (A+E key) form format. It has been painstakingly created for […]

[…] Corporation (IDC) research, NVMe was developed to expedite data transfer to systems connected via PCIe, a serial extension bus used to connect a computer to one or more peripheral […]

[…] and 15 millimeters, is compatible with the newest generation of servers and storage arrays that use PCIe and U.2 backplanes. The DC1500M supports hot plugging, which removes the obstacles associated with […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] PCI Version […]

[…] GT/s. By taking this step, Alphawave is demonstrating that they are prepared to produce chips with a PCIe 6.0 interface and are joining an increasing number of businesses that are laying the groundwork for […]

[…] PCI Version […]