Overview of Agilex 5 FPGAs and SoCs

The Agilex 5 FPGA product line brings the Agilex FPGA portfolio’s advancements to midrange FPGA applications. Numerous applications requiring high performance, reduced power consumption, a smaller form factor, and lower logic densities are catered to by the Agilex 5 FPGAs and SoCs.

Agilex 5 FPGA

- The first AI-enhanced DSP In the industry, Tensor Block provides digital signal processing (DSP) and artificial intelligence (AI) with great efficiency.

- Combining dual-core Arm Cortex-A76 and dual-core Arm Cortex-A55 processors is the first asymmetric applications processor system in the FPGA market, allowing you to maximize processing workload performance and power efficiency.

- With smaller form factor packaging, monolithic die design offers greater system integration and reduced power consumption.

Features of advanced connectivity

- High-speed GTS transceivers with PCI Express (PCIe) up to 28.1 Gbps

- DDR external memory interface up to 4,000 Mbps DDR5 supported via 4.0 ×8

- Overarching goal Voltages supported by I/Os range from 1.0 V to 3.3 V.

Compared to Altera FPGAs from earlier generations, the Agilex 5 FPGA product line offers up to 42% reduced overall power consumption and, on average, 50% better fabric performance.

The product line makes use of the following significant advancements and methods to accomplish this improvement:

Cutting-edge Intel 7 technology

- The Hyperflex FPGA architecture of the second generation

- High degree of system integration

- Options for fixed low core voltage devices and SmartVID

- Power gating, power islands, and other methods of reducing power

The Agilex 5 FPGA product series is perfect for midrange FPGA applications throughout the edge and core because to its sophisticated features and capabilities. Applications cover a wide range of industries, including data centres, industrial, test and measurement, medical electronics, wireless and wireline communications, video and broadcast equipment, and defence.

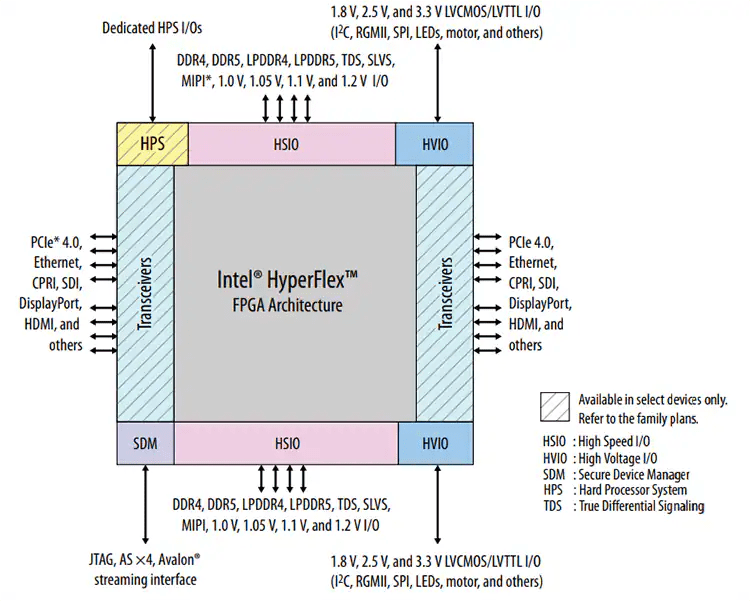

Agilex 5 FPGAs and SoCs Block Diagram

Agilex 5 SoCs

Additional Features for Agilex 5 SoCs

| SoC Subsystem | Feature | Description |

|---|---|---|

| HPS | Multiprocessor unit core | Multicore Arm processors, including dual-core Arm Cortex-A76 MPCore and dual-core Arm Cortex -A55 MPCore processors, with Arm CoreSight debug and trace technologyScalar floating-point unit supporting single and double precisionArm Neon technology media processing engine for each processor |

| System controllers | System memory management unit (SMMU)Cache coherency unit (CCU) | |

| Cache | Arm Cortex -A76:Level 1 cache per core:64 kilobytes (KB) L1 instruction cache with parity64 KB L1 data cache with ECCLevel 2 cache per core: Unified 256 KB L2 data and instructions cache with ECCArm Cortex -A55:Level 1 cache per core:32 KB L1 instruction cache with parity32 KB L1 data cache with ECCLevel 2 cache per core: Unified 128 KB L2 data and instructions cache with ECCShared Level 3 cache: 2 megabytes (MB) L3 cache | |

| On-chip memory | 512 KB on-chip RAM | |

| Direct memory access (DMA) | Eight-channel DMA controller | |

| Ethernet MAC (TSN) | Three 10 Mbps/100 Mbps/1 Gbps/2.5 Gbps Ethernet MACs with integrated DMA and Time-Sensitive Networking (TSN) support1 Gbps and 2.5 Gbps (2.5 Gbps requires soft paths to the transceivers) | |

| USB | One USB 2.0 On-The-Go (OTG) with integrated DMAOne USB 3.1 Gen 1 | |

| UART | Two UART 16550-compatible controllers | |

| Serial peripheral interface (SPI) controller | Four SPI (two masters and two slaves) | |

| I2C | Five I2C controllers | |

| I3C | Two I3C controllers | |

| SD/SDIO/eMMC controller | SD/eMMC devices up to version 5.1SD devices up to version 6.1SDIO devices up to version 4.1 | |

| NAND flash controller | One ONFI 1.x and 2.x8 bit and 16 bit supportCompatible with Toggle 1.x and 2.x specifications | |

| GPIO | Maximum of 48 software-programmable GPIOs | |

| Timers | Four general-purpose timersFive watchdog timers | |

| SDM | Secure bootAES encryptionSecure Hash Algorithms (SHA) and Elliptic Curve Digital Signature Algorithm (ECDSA) authentications | |

| External memory interface | Hard memory controllers :D-Series DDR4, DDR5, LPDDR4, and LPDDR5E-Series:Device Group A DDR4, DDR5, LPDDR4, and LPDDR5Device Group B DDR4, LPDDR4, and LPDDR5 | |